Verilog Coding for Various Digital Circuits (Grade A)

Summary:

This Verilog Coding for Various Digital Circuits note presents Verilog code for a range of digital circuits and components commonly used in digital electronics and computer engineering. The circuits included in the note cover a broad range of functions, from basic arithmetic operations (half-adders, full-adders, half-subtractors, full-subtractors) to more complex functions such as data encoding and decoding (encoders, decoders), signal multiplexing and demultiplexing (multiplexers, demultiplexers), and magnitude comparison (magnitude comparators).

In addition to these basic building blocks, the note also provides Verilog code for various types of flip-flops (SR, D, JK, T) that are fundamental to digital circuits, as well as for counters (synchronous and ripple) that are commonly used for counting and sequencing operations. The note also includes code for shift registers (SISO), which are used to shift digital data from one position to another, and registers (SIPO, PIPO), which are used for storing digital data.

Overall, this note provides a comprehensive collection of Verilog code for digital circuits and components, which can be used by digital electronics and computer engineering students and professionals to implement and simulate various digital circuits and systems.

Excerpt:

Verilog Coding for Various Digital Circuits

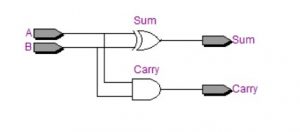

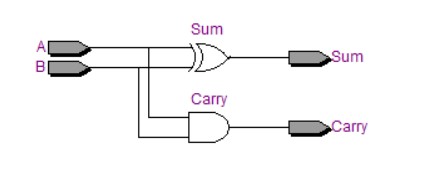

HALF ADDER

Verilog Coding for Various Digital Circuits

module ha(A,B,Sum,Carry);

input A, B;

outputSum, Carry;

assignSum=A^B;

assignCarry=A&B;

end module

Verilog Coding for Various Digital Circuits

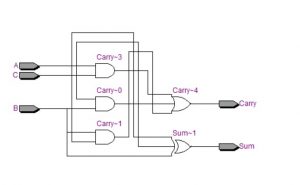

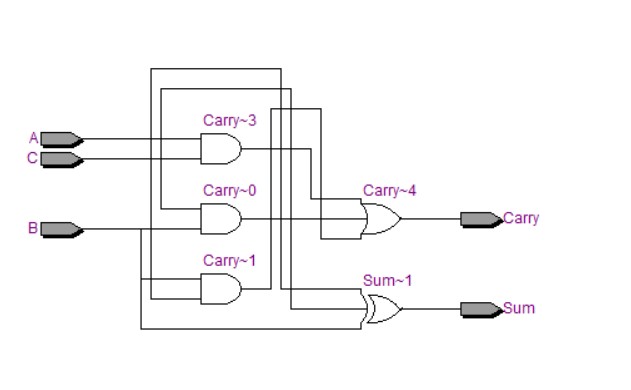

FULL ADDER

Verilog Coding for Various Digital Circuits

module ha(A,B,C,Sum,Carry);

input A, B, C;

outputSum, Carry;

assignSum=A^B^C;

assignCarry=(A&B)|(B&C)|(C&A);

end module

…..

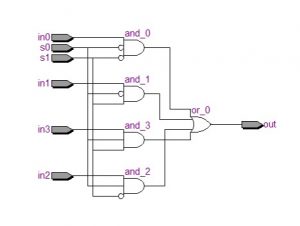

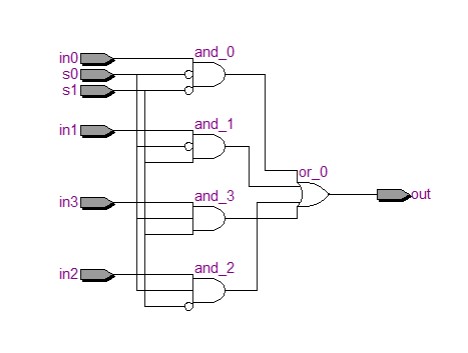

4:1 MULTIPLEXER

Verilog Coding for Various Digital Circuits

modulem31(out,in0,in1,in2,in3,s0,s1);

outputout;//outputport

inputin0,in1,in2,in3;//Inputports

inputs0,s1;//Inputports:selectlines

wireinv0,inv1;//InverterOutputs

wirea0,a1,a2,a3;//ANDgateoutputs

notnot_0(inv0,s0);

notnot_1(inv1,s1);

andand_0(a0,in0,inv0,inv1);

andand_1(a1,in1,inv0,s1);

andand_2(a2,in2,s0,inv1);

andand_3(a3,in3,s0,s1);

oror_0(out,a0,a1,a2,a3);

endmodule

….

modulepro(outputreg[3:0]Y,input[1:0]A,inputdin);

always@(Y,A)begin

case(A)

2’b00:beginY[0]=din;Y[3:1]=0;end

2’b01:beginY[1]=din;Y[0]=0;end

2’b10:beginY[2]=din;Y[1:0]=0;end

2’b11:beginY[3]=din;Y[2:0]=0;end

endcase

end

endmodule

…..

moduledecode(en,s,y);

inputen;

input[1:0]s;

output[3:0]y;

assigny[0]=(~s[1])&(~s[0])&en;

assigny[1]=(~s[1])&(s[0])&en;

assigny[2]=(s[1])&(~s[0])&en;

assigny[3]=(s[1])&(s[0])&en;

endmodule

…..

modulepro(p,q,r,a,b);

input[1:0]a;

input[1:0]b;

outputregp,q,r;

always@(aorb)

begin

if(a===b){p,q,r}=1’b001;

elseif(a>b){p,q,r}=3’b100;

elseif(a<b){p,q,r}=3’b010;

end

endmodule

…..

SRFLIPFLOP

modulepro(s,r,clk,clear,q,qbar);

inputs,r,clk,clear;

outputregq,qbar;

always@(posedgeclk)

begin

if(clear)

begin

q=0;

qbar=1;

end

else

begin

if(s!=r)

begin

q=s;

qbar=r;

end

elseif(s==1&&r==1)

begin

q=1’bz;

qbar=1’bz;

end

end

end

endmodule

…..

DFF

modulepro(d,clk,clear,q,qbar);

inputd,clk,clear;

outputregq,qbar;

always@(posedgeclk)

begin

if(clear==1)

begin

q=0;

qbar=1;

end

else

begin

q=d;

qbar=!d;

end

end

endmodule

Reviews